**DP/HDMI 1:3 De-mux/Mux Switches**

# **Features**

- → DP 1:3 De-Mux or 3:1 Mux switch with 4 high speed differential, AUX/DDC, HPD and CAB\_DET channels

- → Pin selection for 1:3 DEMUX or 3:1 MUX

- → HDMI 3:1 Mux switch with 4 high speed differential, DDC and HPD channels

- → HDMI-mode only supports HDMI-sink application, not support HDMI-source application.

- → Pin selection for DP mode or HDMI mode

- → All ports support up to DP1.2 at 5.4Gb/s or HDMI 2.0 at 6Gb/s

- Supports manual switching or HPD auto priority selection → in 1:3 DEMUX, in DP mode

- → Low current consumption

- 3.3V power supply →

- ESD protection on all I/O pins for 2kV HBM →

- Package: →

60 pin TQFN (5x9mm)

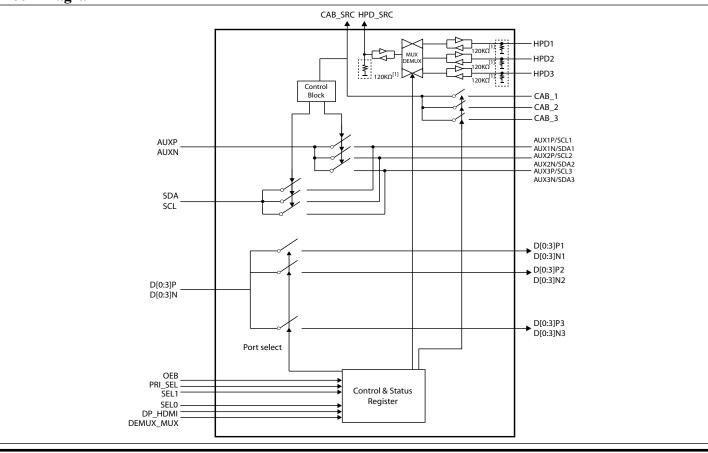

#### **Block Diagram**

# Description

The PI3WVR31310A is a 3:1 Mux or 1:3 Demux high speed passive switch supporting DP 1.2, HDMI 1.4, HDMI 2.0. At DEMUX mode, all three output ports support auto port priority selection by detecting HPD1/2/3 input or manual selection. At MUX mode, HPD1/2/3 will change from input to output, there is no auto port priority selection.

### **Application**

→ Notebook, Monitor, Switch box or TV sink application

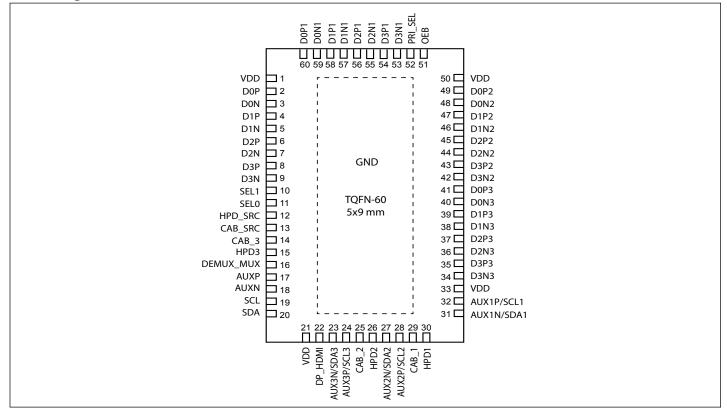

#### **Pin Configuration: TQFN-60**

17-0002

# **Pin Description**

| pin# | pin Name | Signal Type | Description                                        |  |  |  |

|------|----------|-------------|----------------------------------------------------|--|--|--|

| 2,   | D0P,     |             |                                                    |  |  |  |

| 4,   | D1P,     |             |                                                    |  |  |  |

| 6,   | D2P,     |             |                                                    |  |  |  |

| 8,   | D3P,     | IO          | 4 differential pair I/O (DP or HDMI)               |  |  |  |

| 3,   | D0N,     | IO          |                                                    |  |  |  |

| 5,   | D1N,     |             |                                                    |  |  |  |

| 7,   | D2N,     |             |                                                    |  |  |  |

| 9    | D3N      |             |                                                    |  |  |  |

| 60,  | D0P1,    |             |                                                    |  |  |  |

| 58,  | D1P1,    |             |                                                    |  |  |  |

| 56,  | D2P1,    |             |                                                    |  |  |  |

| 54,  | D3P1,    | IO          | 4 differential main L/Q (DD on LID)(1) for most 1  |  |  |  |

| 59,  | D0N1,    | IO          | 4 differential pair I/O (DP or HDMI) for port 1    |  |  |  |

| 57,  | D1N1,    |             |                                                    |  |  |  |

| 55,  | D2N1,    |             |                                                    |  |  |  |

| 53   | D3N1     |             |                                                    |  |  |  |

| 49,  | D0P2,    |             |                                                    |  |  |  |

| 47,  | D1P2,    |             |                                                    |  |  |  |

| 45,  | D2P2,    |             |                                                    |  |  |  |

| 43,  | D3P2,    | IO          | 1 differential main I/O (DD on UD)(I) for most 2   |  |  |  |

| 48,  | D0N2,    | IO          | 4 differential pair I/O (DP or HDMI) for port 2    |  |  |  |

| 46,  | D1N2,    |             |                                                    |  |  |  |

| 44,  | D2N2,    |             |                                                    |  |  |  |

| 42   | D3N2     |             |                                                    |  |  |  |

| 41,  | D0P3,    |             |                                                    |  |  |  |

| 39,  | D1P3,    |             |                                                    |  |  |  |

| 37,  | D2P3,    |             |                                                    |  |  |  |

| 35,  | D3P3,    |             | 4 differential main L/O (DD on LID) (1) for mont 2 |  |  |  |

| 40,  | D0N3,    | IO          | 4 differential pair I/O (DP or HDMI) for port 3    |  |  |  |

| 38,  | D1N3,    |             |                                                    |  |  |  |

| 36,  | D2N3,    |             |                                                    |  |  |  |

| 34   | D3N3     |             |                                                    |  |  |  |

| pin#          | pin Name    | Signal Type | Description                                                                                                                                                                             |

|---------------|-------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31,           | AUX1N/SDA1, |             |                                                                                                                                                                                         |

| 27,           | AUX2N/SDA2, |             |                                                                                                                                                                                         |

| 23,           | AUX3N/SDA3, | 10          |                                                                                                                                                                                         |

| 32,           | AUX1P/SCL1, | IO          | AUX (DP) or DDC (HDMI) input from three ports                                                                                                                                           |

| 28,           | AUX2P/SCL2, |             |                                                                                                                                                                                         |

| 24            | AUX3P/SCL3  |             |                                                                                                                                                                                         |

| 18,           | AUXN,       | 10          |                                                                                                                                                                                         |

| 17            | AUXP        | IO          | AUX output                                                                                                                                                                              |

| 20,           | SDA,        | 10          |                                                                                                                                                                                         |

| 19            | SCL         | IO          | DDC output                                                                                                                                                                              |

| 30,           | HPD1,       |             | When DEMUX_MUX = low (1:3 DEMUX mode), HPD1_2_3                                                                                                                                         |

| 26,           | HPD2,       | 10          | are inputs, HPD_SRC is output;                                                                                                                                                          |

| 15,           | HPD3,       | IO          | When DEMUX_MUX = high (3:1 MUX mode), HPD1_2_3 are                                                                                                                                      |

| 12            | HPD_SRC     |             | outputs, HPD_SRC is input                                                                                                                                                               |

| 29,           | CAB_1,      |             |                                                                                                                                                                                         |

| 25,           | CAB_2,      | ю           | CAR I CAR 2 CAR 2 CAR SEC                                                                                                                                                               |

| 14,           | CAB_3,      | IO          | CAB_1, CAB_2, CAB_3, CAB_SRC                                                                                                                                                            |

| 13            | CAB_SRC     |             |                                                                                                                                                                                         |

| 51            | OEB         | Ι           | OEB=0, device active; OEB=1, device shut down                                                                                                                                           |

| 52            | PRI_SEL     | Ι           | PRI_SEL is for priority selection as in priority-selection-table,<br>but only for 1:3 DEMUX mode. PRI_SEL has internal 100K<br>divider between VDD and GND for middle-state with VDD/2. |

| 16            | DEMUX_MUX   | Ι           | DEMUX_MUX is for HPD direction selection, see truth table                                                                                                                               |

| 22            | DP_HDMI     | Ι           | DP port or HDMI port, see truth table                                                                                                                                                   |

| 11            | SELO        | Ι           | Port selection pins, see truth table                                                                                                                                                    |

| 10            | SEL1        | Ι           | Port selection pins, see truth table                                                                                                                                                    |

| 1, 21, 33, 50 | VDD         | Power       | 3.3V VDD                                                                                                                                                                                |

| Center Pad    | GND         | Ground      | Bottom GND EPAD                                                                                                                                                                         |

| m merting for sum more 21 source 21 or the |               |                         |                           |                           |                           |            |  |  |  |

|--------------------------------------------|---------------|-------------------------|---------------------------|---------------------------|---------------------------|------------|--|--|--|

| DP mode                                    | HDMI/DVI mode | WVR31310A<br>input pins | WVR31310A<br>port1 output | WVR31310A<br>port2 output | WVR31310A<br>port3 output | DP mode    |  |  |  |

| ML_lan0(P)                                 | TX2+          | D0P                     | D0P1                      | D0P2                      | D0P3                      | ML_lan0(P) |  |  |  |

| ML_lan0(N)                                 | TX2-          | D0N                     | D0N1                      | D0N2                      | D0N3                      | ML_lan0(N) |  |  |  |

| ML_lan1(P)                                 | TX1+          | D1P                     | D1P1                      | D1P2                      | D1P3                      | ML_lan1(P) |  |  |  |

| ML_lan1(N)                                 | TX1-          | D1N                     | D1N1                      | D1N2                      | D1N3                      | ML_lan1(N) |  |  |  |

| ML_lan2(P)                                 | TX0+          | D2P                     | D2P1                      | D2P2                      | D2P3                      | ML_lan2(P) |  |  |  |

| ML_lan2(N)                                 | ТХ0-          | D2N                     | D2N1                      | D2N2                      | D2N3                      | ML_lan2(N) |  |  |  |

| ML_lan3(P)                                 | TXC+          | D3P                     | D3P1                      | D3P2                      | D3P3                      | ML_lan3(P) |  |  |  |

| ML_lan3(N)                                 | TXC-          | D3N                     | D3N1                      | D3N2                      | D3N3                      | ML_lan3(N) |  |  |  |

### Pin mapping for dual mode DP source DEMUX to DP output

# **Function Description**

Default input format is DP. DP\_HDMI can select between DP or HDMI input.

In Demux mode, there are 120K pull down in HPD1/HPD2/HPD3 pins. In Mux mode, there is 120K pull down in HPD\_SRC pin.

Output port can be selected by manual or automatically in DEMUX mode.

Automatic port selection is done by detection of HPD presence from the output ports. If multiple HPD are detected, port selection depends on a priority scheme defined by PRI\_SEL pin. There can be 3 priority schemes. When PRI\_SEL=low, the port priority order is port1/port2/port3; when PRI\_SEL=high, the port priority order is port2/port3/port1; when PRI\_SEL=M (open), the port priority order is port3/port1/port2.

When port 1 or port 2 or port 3 is selected in DP application, and CAB=LOW, AUX/DDC input pins are now AUX channel. AUXP will have 100Kohm resistor to GND while AUXN will have 100Kohm resistor to VDD in external port side. Max. AUX data rate can be 720Mb/s. DDC switch inside is off.

When port 1 or port 2 or port 3 is active in dual mode DP or HDMI application, and CAB=HIGH, AUX/DDC input pins are now DDC channel. AUX switch inside is off, DDC switch is on. The DDC switch can support 5V input, and output Vpass is less than 3.3V limit.

HPD is CMOS buffer, and support 5v inputs. When used as DEMUX, There're 120kΩ pull-down resistors inside connected to HPD1, HPD2, HPD3 as input, and when used as MUX, 120k resistor connected to HPD\_SRC as input.

### **Truth Table**

#### DEMUX\_MUX

| DEMUX_MUX | HPD_SRC | HPD1/2/3 |

|-----------|---------|----------|

| 0 (DEMUX) | output  | input    |

| 1 (MUX)   | input   | output   |

| DP_HDMI |           |  |  |  |  |

|---------|-----------|--|--|--|--|

| DP_HDMI | Mode      |  |  |  |  |

| 0       | DP Mode   |  |  |  |  |

| 1       | HDMI Mode |  |  |  |  |

#### SLE1/SEL0 in 1:3 DP modes

|      |      | PRI_SEL              |                    |                           |

|------|------|----------------------|--------------------|---------------------------|

| SEL1 | SEL0 | (priority selection) | HPD/CAB_DET        | D[0:3]P, D[0:3]N, AUX/DDC |

| 0    | 0    | NC                   | HPD1/CAB_1         | Port 1                    |

| 0    | 1    | NC                   | HPD2/CAB_2         | Port 2                    |

| 1    | 0    | NC                   | HPD3/CAB_3         | Port 3                    |

| 1    | 1    | Auto-selection       | See priority table | See priority table        |

#### SLE1/SEL0 in 3:1 HDMI mode and DP mode

| SEL1 | SELO | PRI_SEL<br>(priority selection) | HPD                | D[0:3]P, D[0:3]N, AUX/DDC |

|------|------|---------------------------------|--------------------|---------------------------|

| 0    | 0    | NC                              | HPD=HPD1, HPD2/3=0 | Port 1                    |

| 0    | 1    | NC                              | HPD=HPD2, HPD1/3=0 | Port 2                    |

| 1    | 0    | NC                              | HPD=HPD3, HPD1/2=0 | Port 3                    |

| 1    | 1    | NC                              | NC                 | NC                        |

#### AUX and DDC

| PORT                   | DP_HDMI | CAB_1 | CAB_2 | CAB_3                          | AUXP  | AUXN  | SCL  | SDA  |

|------------------------|---------|-------|-------|--------------------------------|-------|-------|------|------|

|                        | 0       | 0     | x     | x                              | AUX1P | AUX1N | Hi-Z | Hi-Z |

| When Port1<br>Selected | 0       | 1     | x     | x                              | Hi-Z  | Hi-Z  | SCL1 | SDA1 |

| beleeted               | 1       | 1     | x     | x                              | Hi-Z  | Hi-Z  | SCL1 | SDA1 |

|                        | 0       | x     | 0     | x                              | AUX2P | AUX2N | Hi-Z | Hi-Z |

| When Port2<br>Selected | 0       | x     | 1     | x                              | Hi-Z  | Hi-Z  | SCL2 | SDA2 |

| Selected               | 1       | x     | 1     | x AUX2P AUX2N Hi-<br>x Hi-Z SC | SCL2  | SDA2  |      |      |

|                        | 0       | x     | x     | 0                              | AUX3P | AUX3N | Hi-Z | Hi-Z |

| When Port3<br>Selected | 0       | x     | X     | 1                              | Hi-Z  | Hi-Z  | SCL3 | SDA3 |

| Genered                | 1       | x     | X     | 1                              | Hi-Z  | Hi-Z  | SCL3 | SDA3 |

#### All trademarks are property of their respective owners.

### **Priority Selection Table**

| PRI_SEL<br>(Priority order) | HPD1 | HPD2 | HPD3 | HPD_SRC | CAB_SRC          | AUXP/AUXN   | SDA/SCL   |

|-----------------------------|------|------|------|---------|------------------|-------------|-----------|

| 0                           | 0    | 0    | 0    | 0       | Hi-Z             | Hi-Z        | Hi-Z      |

| 0                           | 1    | x    | x    | HPD1    | CAB1             | AUX1P/AUX1N | SDA1/SCL1 |

| 0                           | 0    | 1    | x    | HPD2    | CAB2             | AUX2P/AUX2N | SDA2/SCL2 |

| 0                           | 0    | 0    | 1    | HPD3    | CAB3             | AUX3P/AUX3N | SDA3/SCL3 |

| М                           | 0    | 0    | 0    | 0       | Hi-Z             | Hi-Z        | Hi-Z      |

| М                           | 1    | x    | 0    | HPD1    | CAB1             | AUX1P/AUX1N | SDA1/SCL1 |

| М                           | 0    | 1    | 0    | HPD2    | CAB2             | AUX2P/AUX2N | SDA2/SCL2 |

| М                           | x    | x    | 1    | HPD3    | CAB3             | AUX3P/AUX3N | SDA3/SCL3 |

| 1                           | 0    | 0    | 0    | 0       | Hi-Z             | Hi-Z        | Hi-Z      |

| 1                           | 1    | 0    | 0    | HPD1    | CAB1             | AUX1P/AUX1N | SDA1/SCL1 |

| 1                           | x    | 1    | x    | HPD2    | CAB2 AUX2P/AUX   |             | SDA2/SCL2 |

| 1                           | x    | 0    | 1    | HPD3    | CAB3 AUX3P/AUX3N |             | SDA3/SCL3 |

Note: M= VDD/2 or open (with internal VDD/2)

| PRI_SEL          |      |      |      |      |      |      |      |      |      |      |      |

|------------------|------|------|------|------|------|------|------|------|------|------|------|

| (Priority order) | HPD1 | HPD2 | HPD3 | DOP  | D1P  | D2P  | D3P  | D0N  | D1N  | D2N  | D3N  |

| 0                | 0    | 0    | 0    | Hi-Z |

| 0                | 1    | x    | x    | D0P1 | D1P1 | D2P1 | D3P1 | D0N1 | D1N1 | D2N1 | D3N1 |

| 0                | 0    | 1    | x    | D0P2 | D1P2 | D2P2 | D3P2 | D0N2 | D1N2 | D2N2 | D3N2 |

| 0                | 0    | 0    | 1    | D0P3 | D1P3 | D2P3 | D3P3 | D0N3 | D1N3 | D2N3 | D3P3 |

| М                | 0    | 0    | 0    | Hi-Z |

| М                | 1    | x    | 0    | D0P1 | D1P1 | D2P1 | D3P1 | D0N1 | D1N1 | D2N1 | D3N1 |

| М                | 0    | 1    | 0    | D0P2 | D1P2 | D2P2 | D3P2 | D0N2 | D1N2 | D2N2 | D3N2 |

| М                | x    | x    | 1    | D0P3 | D1P3 | D2P3 | D3P3 | D0N3 | D1N3 | D2N3 | D3P3 |

| 1                | 0    | 0    | 0    | Hi-Z |

| 1                | 1    | 0    | 0    | D0P1 | D1P1 | D2P1 | D3P1 | D0N1 | D1N1 | D2N1 | D3N1 |

| 1                | x    | 1    | x    | D0P2 | D1P2 | D2P2 | D3P2 | D0N2 | D1N2 | D2N2 | D3N2 |

| 1                | x    | 0    | 1    | D0P3 | D1P3 | D2P3 | D3P3 | D0N3 | D1N3 | D2N3 | D3P3 |

Note: M= VDD/2 or open (with internal VDD/2)

Note: For priority selection control, when PRI\_SEL = 0, the order is port1/port2/port3; when PRI\_SEL = 1, the order is port2/port3/port1; when PRI\_SEL = M, the order is port3/port1/port2.

# **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines not tested.)

|                                                          | L |

|----------------------------------------------------------|---|

| Storage Temperature65°C to +150°C                        |   |

| Supply Voltage to Ground Potential0.5V to +4.6V          |   |

| High Speed Channel Input Voltage (DP Mode)0.5V to 2V     |   |

| High Speed Channel Input Voltage (HDMI Mode)2.4V to 3.6V |   |

| DDC and HPD channels Input Voltage0.5V to 6V             |   |

| DC Output Current                                        |   |

| Power Dissipation                                        |   |

|                                                          | L |

Note: Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **Electrical Characteristics**

# **Recommended Operation Conditions**

$V_{DD} = 3.3V \pm 10\%$ , Min and Max apply for TA between -40°C to 85°C Typical values are referenced to TA = 25°C

| Parameter       | Description                     | Test Conditions                 | Min. | Typ. | Max. | Unit |

|-----------------|---------------------------------|---------------------------------|------|------|------|------|

| V <sub>DD</sub> | Operating Voltage               |                                 | 3.0  | 3.3  | 3.6  | V    |

| I <sub>DD</sub> | VDD supply current              | V <sub>DD</sub> =3.3V           |      | 1    |      | mA   |

|                 | Supply current when OEB disable | V <sub>DD</sub> =3.6V, OEB=high |      | 0.7  |      | A    |

| Istd            | HDMI Mode                       | DP_HDMI=1                       | 0.7  |      |      | mA   |

| Ista            | Supply current when OEB disable | V <sub>DD</sub> =3.6V, OEB=high |      | 10   |      |      |

|                 | DP Mode                         | DP_HDMI=0                       |      | 10   |      | uA   |

# **DC Electrical Characteristics for Switching over Operating Range**

| Parameter       | Description                         | Test Conditions                  | Min.   | Typ. | Max.   | Unit |

|-----------------|-------------------------------------|----------------------------------|--------|------|--------|------|

| OEB, SEL1, SE   | ELO                                 |                                  |        |      | ·      |      |

| I <sub>IH</sub> | High level digital input current    | V <sub>IH</sub> =V <sub>DD</sub> | -10    |      | 40     | μA   |

| I <sub>IL</sub> | Low level digital input current     | $V_{IL} = GND$                   | -10    |      | 10     | μA   |

| V <sub>IH</sub> | High level digital input voltage    |                                  | 2.0    |      |        | V    |

| V <sub>IL</sub> | Low level digital input voltage     |                                  | 0      |      | 0.8    | V    |

| DEMUX_MU        | X                                   |                                  |        |      |        |      |

| I <sub>IH</sub> | High level digital input current    | V <sub>IH</sub> =VDD             | -10    |      | 40     | μA   |

| I <sub>IL</sub> | Low level digital input current     | V <sub>IL</sub> = GND            | -10    |      | 10     | μA   |

| V <sub>IH</sub> | High level digital input voltage    |                                  | 2.7    |      |        | V    |

| V <sub>IL</sub> | Low level digital input voltage     |                                  | 0      |      | 0.8    | V    |

| DP_HDMI         |                                     |                                  |        |      |        |      |

| R <sub>pd</sub> | Inter Pull-down resistor on DP_HDMI |                                  |        | 100  |        | kΩ   |

| V <sub>IH</sub> | High level digital input voltage    |                                  | 0.7Vdd |      |        | V    |

| V <sub>IL</sub> | Low level digital input voltage     |                                  | 0      |      | 0.3Vdd | V    |

| Parameter                | Description                                            | Test Conditions                                                      | Min.     | Typ. | Max. | Unit |

|--------------------------|--------------------------------------------------------|----------------------------------------------------------------------|----------|------|------|------|

| HPD_SRC (wh              | en HPD_SRC is output, HPD 1, 2                         | 2, 3 are inputs)                                                     |          |      |      |      |

| V <sub>IH</sub>          | High level digital input voltage                       | V <sub>DD</sub> =3.3V                                                | 2.0      |      |      | V    |

| V <sub>IL</sub>          | Low level digital input voltage                        | V <sub>DD</sub> =3.3V                                                | 0        |      | 0.8  | V    |

| V <sub>OL_HPD_SRC</sub>  | Buffer Output Low Voltage                              | $I_{OL} = 4 \text{ mA}$                                              |          |      | 0.4  | V    |

| V <sub>OH_HPD_SRC</sub>  | Buffer Output Low Voltage                              | $I_{OH} = 4 \text{ mA}$                                              | 2.4      |      |      | V    |

| HPD_Sink (wł             | nen HPD_SRC is input, HPD 1, 2                         | , 3 are as sink outputs)                                             |          |      |      |      |

| V <sub>IH</sub>          | High level digital input voltage                       |                                                                      | 2.0      |      |      | V    |

| V <sub>IL</sub>          | Low level digital input voltage                        | $V_{DD}=3.3V$                                                        | 0        |      | 0.8  | V    |

| V <sub>OL_HPD_Sink</sub> | Buffer Output Low Voltage                              | $I_{OL} = 4 \text{ mA}$                                              |          |      | 0.4  | V    |

| V <sub>OH_HPD_Sink</sub> | Buffer Output Low Voltage                              | $I_{OH} = 4 \text{ mA}$                                              | 2.4      |      |      | V    |

| САВ                      |                                                        | 1                                                                    |          | I    | 1    |      |

| I <sub>LK</sub>          | Input leakage current                                  | Switch is off, Vin=5.5V                                              | -50      |      | 50   | uA   |

| C <sub>IO</sub>          | Input/Output capacitance when passive switch on        |                                                                      |          | 10   |      | pF   |

| R <sub>ON</sub>          | Passive Switch resistance                              | $I_{O} = 3mA, V_{O} = 0.4V$                                          |          | 25   | 50   | Ω    |

| V <sub>pass</sub>        | Switch Output voltage                                  | V <sub>I</sub> =3.3V, I <sub>I</sub> =100uA                          | 3.0      |      | 4.0  | V    |

| CI(source)               | Source side CAB capacitance                            |                                                                      |          | 3.5  |      | pF   |

| CI(sink)                 | Sink side CAB capacitance when                         | $V_{I}$ peak-peak = 1V, 100 KHz                                      |          | 6.5  |      | pF   |

| SDA/SCL,SDA1             | /SCL1, SDA2/SCL2 , SDA3/SCL3 (pa                       | assive switch)                                                       |          |      |      |      |

| I <sub>LK</sub>          | Input leakage current                                  | DDC switch is off, Vin=5.5V                                          | -50      |      | 50   | uA   |

| C <sub>IO</sub>          | Input/Output capacitance when passive switch on        | $V_I$ peak-peak = 1V, 100 KHz                                        |          | 10   |      | pF   |

| R <sub>ON</sub>          | Passive Switch resistance                              | $I_{O} = 3mA, V_{O} = 0.4V$                                          |          | 25   | 50   | Ω    |

| Vesse                    | Switch Output wiltow                                   | V <sub>I</sub> =5.0V, I <sub>I</sub> =100uA                          | 1.5      | 2.0  | 2.5  | V    |

| Vpass                    | Switch Output voltage                                  | V <sub>DD</sub> =3.3V                                                | 1.5      |      |      | v    |

| CI(source)               | Source side DDC capacitance (<br>passive switch off. ) | $V_{I}$ peak-peak = 1V, 100 KHz                                      |          | 2.5  |      | pF   |

| CI(sink)                 | Sink side DDC capacitance (pas-<br>sive switch off.)   | $V_{I}$ peak-peak = 1V, 100 KHz                                      |          | 9    |      | pF   |

| AUXP, AUXN, A            | AUXnP/SCLn, AUXnN/SDAn                                 |                                                                      |          |      |      |      |

| I <sub>LK</sub>          | Input leakage current                                  | DDC switch is off, Vin=5.5V                                          | 5.5V -50 |      | 50   | uA   |

| C <sub>IO</sub>          | Input/Output capacitance when passive switch on        | V <sub>I</sub> peak-peak = 1V, 100 KHz                               |          | 7    |      | pF   |

| R <sub>ON</sub>          | Passive Switch resistance                              | $I_{O} = 3mA, V_{O} = 0.4V$                                          |          | 5    | 15   | Ω    |

| V <sub>pass</sub>        | Switch Output voltage                                  | V <sub>I</sub> =5.5V, I <sub>I</sub> =100uA<br>V <sub>DD</sub> =3.3V | 3.0      | 4.0  | 4.5  | V    |

| CI(source)               | Source side capacitance ( passive switch off. )        | V <sub>I</sub> peak-peak = 1V, 100 KHz                               |          | 2.5  |      | pF   |

9

All trademarks are property of their respective owners.

| Parameter            | Description                                                       | Test Conditions                                                                                                    | Min. | Тур. | Max. | Unit |

|----------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| CI(sink)             | Sink side capacitance ( passive switch off. )                     | V <sub>I</sub> peak-peak = 1V, 100 KHz                                                                             |      | 3.5  |      | pF   |

| High Speed Cha       | nnel (D[0:3]P/N – D[0:3]P1N1, D[0:                                | 3]P/N – D[0:3]P2N2)                                                                                                |      |      |      |      |

| V <sub>IK</sub>      | Clamp Diode Voltage (HS Chan-<br>nel)                             | - V <sub>DD</sub> = Max., I <sub>IN</sub> = -18mA -1.6                                                             |      | -1.8 | V    |      |

| I <sub>IH</sub>      | Input HIGH Current                                                | $V_{DD} = Max., V_{IN} = V_{DD}$                                                                                   |      |      | ±10  |      |

| I <sub>IL</sub>      | Input LOW Current                                                 | $V_{DD} = Max., V_{IN} = GND$                                                                                      |      |      | ±10  | μA   |

| R <sub>ON_HS</sub>   | On resistance between input to<br>out- put for high speed signals | $V_{INPUT,cm} = 0V \text{ to } 0.8V,$ $V_{INPUT, diff} < 1.0V_{p-p,diff},$ $V_{DD} = 3.0V, I_{INPUT} = 20mA$       |      | 8    | 12   | Ohm  |

|                      |                                                                   | $V_{INPUT,cm} = 2.2V \text{ to } 3.1V,$ $V_{INPUT, diff} < 1.2Vp\text{-p,diff},$ $V_{DD} = 3.0V, I_{INPUT} = 20mA$ |      | 8    | 12   | Ohm  |

| Input signal voltage | HDMI MUX mode                                                     | Channel on                                                                                                         | 2.4  |      | 3.3  | V    |

| range                | HDMI MUX mode                                                     | Channel off                                                                                                        | 0    |      | 3.3  | V    |

Note: High speed channel does not support Ioff when VDD=0

#### All trademarks are property of their respective owners.

17-0002

10

# **Dynamic Electrical Characteristics**

| Parameter             | Description                                                              | scription Test Conditions                                                  |             | Min. | Typ. <sup>(1)</sup> | Max. | Unit |

|-----------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------|------|---------------------|------|------|

| SCL, SDA cha          | nnel, AUX channel, CAB channel (passive                                  | switch)                                                                    |             |      |                     |      |      |

|                       | Propagation delay from SCLn/SDAn to                                      | $C_{\rm L}$ = 10pF, in passive switch                                      |             |      |                     | 5    |      |

| t <sub>pd</sub> (DDC) |                                                                          |                                                                            |             |      | 60                  | ns   |      |

| Control and           | Status Pins (HPDn, HPD_SRC)                                              |                                                                            |             |      |                     |      |      |

| tpd(HPD)              | Propagation delay (from HPDx to the active port of HPD_SRC, high to low) | $C_L = 10$ pF, manual selection<br>mode; auto mode refer to auto<br>timing |             |      | 10                  |      | ns   |

| tsx(HPD)              | Switch time (from port select to the latest HPD )                        |                                                                            |             |      | 5                   |      | us   |

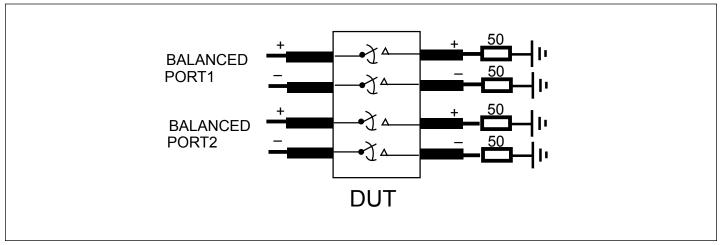

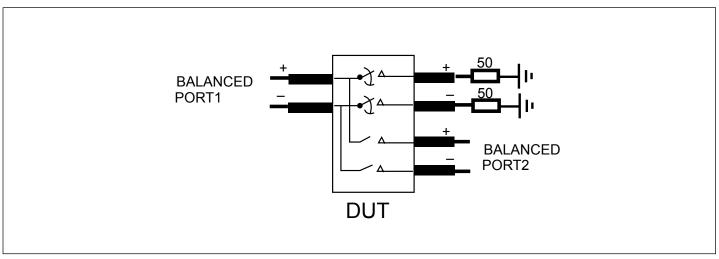

| V                     | Crosstalk on High Speed Channels                                         | See Fig.1 for<br>Measurement                                               | f = 2.7 GHz |      | -26                 | -23  |      |

| X <sub>TALK</sub>     |                                                                          | Setup                                                                      | f = 3.0 GHz |      | -24                 | -21  | 10   |

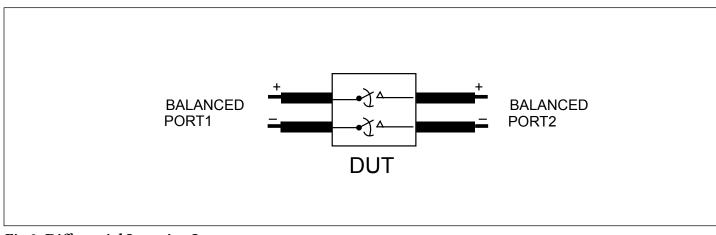

| O <sub>IRR</sub>      | OFF Isolation on High Speed Channels                                     |                                                                            | f = 2.7 GHz |      | -21                 | -19  | dB   |

|                       |                                                                          |                                                                            | f = 3.0 GHz |      | -21                 | -19  |      |

| I <sub>LOSS</sub>     | Differential Insertion Loss on High speed channels                       | @5.4Gbps (see figure 3, Vcom<br>= 0V)                                      |             | -1.8 | -1.6                |      | dB   |

| I <sub>LOSS</sub>     | Differential Insertion Loss on High<br>Speed HDMI Channels               | <pre>@6Gbps (see figure 3, Vcom = 3.0V)</pre>                              |             |      | -2.5                |      | dB   |

| R <sub>loss</sub>     | Differential Return Loss on High speed channels                          | @ 2.7GHz (5.4Gbps)                                                         |             |      | -18                 | -15  | dB   |

| BW_Dx±                | Bandwidth -3dB for Main High speed<br>path (Dx±)                         | See figure 3                                                               |             | 5.0  | 5.4                 |      | GHz  |

| BW_Dx±                | Bandwidth -3dB for Main high speed<br>HDMI path (Dx±)                    | See figure 3                                                               |             | 4.7  | 5.0                 |      | GHz  |

| BW_AUX                | Bandwidth -3dB for AUX                                                   | See figure 3                                                               |             | 1.2  | 1.5                 |      | GHz  |

| Tsw a-b               | time it takes to switch from port A to port B                            | Manual selection                                                           |             |      |                     | 1    | us   |

| Tsw b-a               | time it takes to switch from port B to port A                            | Manual selection                                                           |             |      |                     | 1    | us   |

| T <sub>startup</sub>  | Vdd valid to channel enable                                              | Manual selection                                                           |             |      |                     | 10   | us   |

| T <sub>wakeup</sub>   | Enabling output by changing OEB from High to Low                         | Manual selection                                                           |             |      |                     | 10   | us   |

# Fig 1. Crosstalk Setup

Fig 2. Off-isolation setup

Fig 3. Differential Insertion Loss

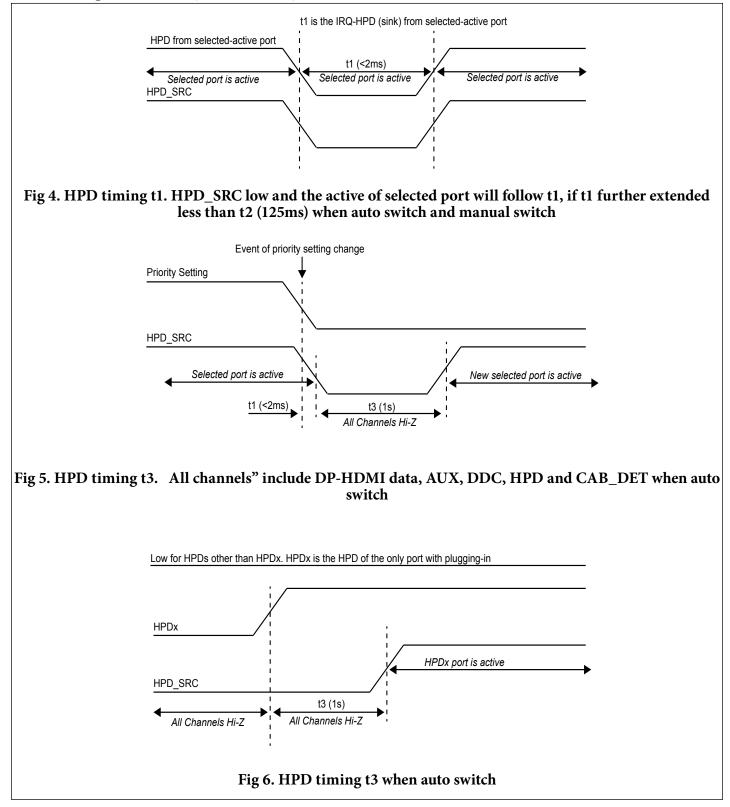

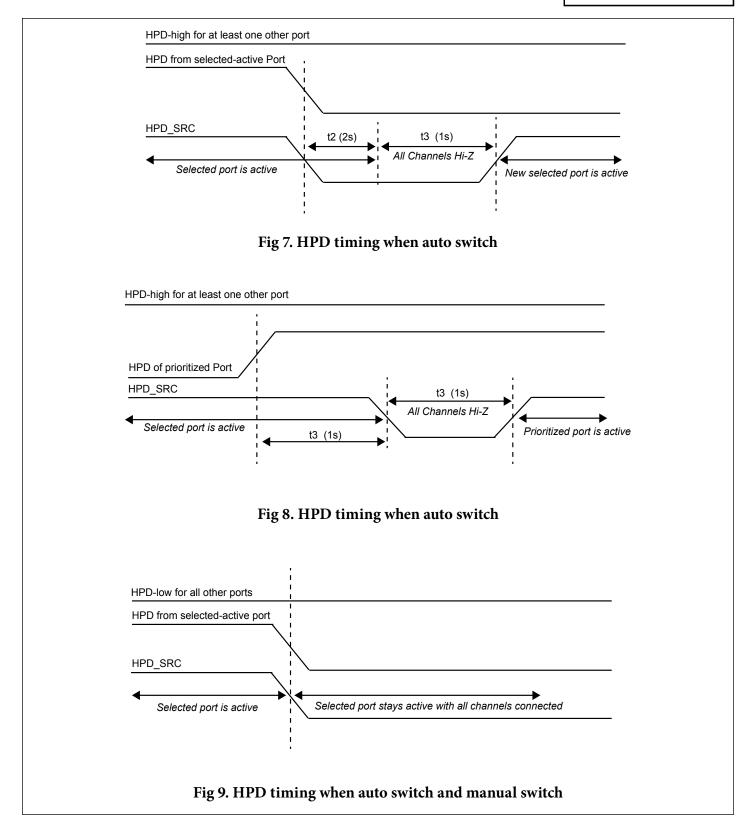

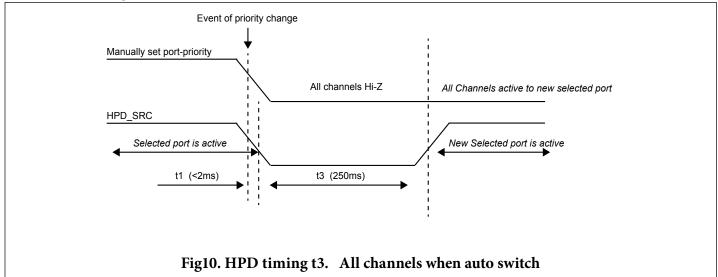

### HPD timing waveform (DEMUX mode)

### **Port Selection by Manual Mode**

| Parameter                                                                      | Test Conditions | Min. | Тур.* | Max. | Unit |

|--------------------------------------------------------------------------------|-----------------|------|-------|------|------|

| HPD auto switching timing                                                      |                 |      |       |      |      |

| HPD pulse duration when treated as an IRQ -t1 (Figure 4)                       |                 |      |       | 2    | ms   |

| Propagation delay of HPDx Desertion -t2 (Figure 7)                             |                 | 1.2s | 2s    | 3s   | s    |

| HPD_SRC low duration when the outputs are switched -t3(Figure 5, 6, 7, 8, 10); |                 | 0.6s | 1s    | 1.5s | S    |

| Propagation delay of HPDx assertion (Figure 8)                                 |                 |      |       |      |      |

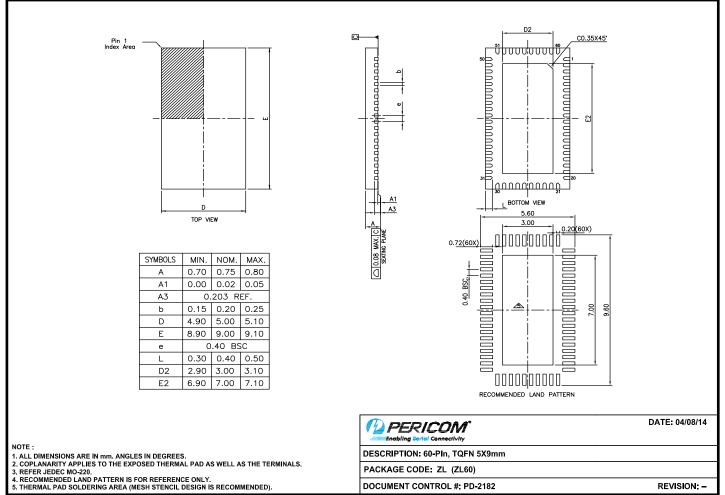

# **Packaging Mechanical: ZL60**

14-0044

Note: For latest package info, please check: http://www.pericom.com/support/packaging/packaging-mechanicals-and-thermal-characteristics/

### **Ordering Information**

| Ordering Code    | Package Code | Package Description               |

|------------------|--------------|-----------------------------------|

| PI3WVR31310AZLE  | ZL           | 60-Pin, (TQFN) 5X9mm              |

| PI3WVR31310AZLEX | ZL           | 60-Pin, (TQFN) 5X9mm, Tape & Reel |

#### Notes:

• Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

• "E" denotes Pb-free and Green

• Adding an "X" at the end of the ordering code denotes tape and reel packaging

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

A. Life support devices or systems are devices or systems which:

1. are intended to implant into the body, or

2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the

failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated

www.diodes.com

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Diodes Incorporated: <u>PI3WVR31310AZLEX</u>